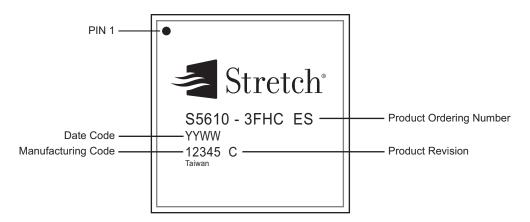

**\$5610**Data Sheet

Version 1.7

© 2005 Stretch, Inc. All rights reserved. The Stretch logo, Stretch, and Extending the Possibilities are trademarks of Stretch, Inc. All other trademarks and brand names are the properties of their respective owners.

This preliminary publication is provided "AS IS." Stretch, Inc. (hereafter "Stretch") DOES NOT MAKE ANY WARRANTY OF ANY KIND, EITHER EXPRESSED OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF TITLE, NONINFRINGEMENT, MERCHANT-ABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Information in this document is provided solely to enable system and software developers to use Stretch S5000 processors. Unless specifically set forth herein, there are no express or implied patent, copyright or any other intellectual property rights or licenses granted hereunder. Stretch does not warrant that the contents of this publication, whether individually or as one or more groups, meets your requirements or that the publication is error-free. This publication could include technical inaccuracies or typographical errors. Changes may be made to the information herein, and these changes may be incorporated in new editions of this publication.

Part #: DS-5610-0001-007

# **Changes from Previous Release**

| Release | Chapter                                 | Change                                  |

|---------|-----------------------------------------|-----------------------------------------|

| 1.7     | Chapter 3, "Electrical Characteristics" | Updated Voн, Vol, Voнт, Volt conditions |

Version 1.7 Last modified: 07/12/2006

# \$5610 at a Glance

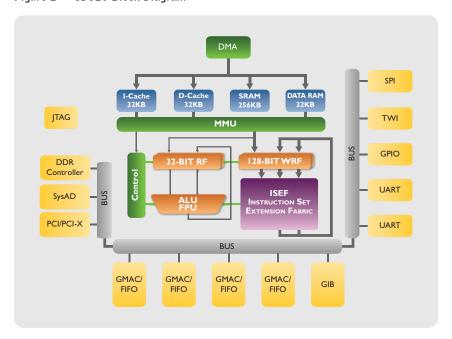

This document highlights the features and peripheral devices that constitute the S5610 processor. For full details on each peripheral device refer to the *S5000 Peripheral Reference*. Figure 1 on the following page is a block diagram of the S5610 processor.

#### **Processor Features**

- 300 MHz, 32-bit Xtensa® core processor

- 16- and 24-bit instructions

- MMU with TLB

- Single-precision floating point operations

- Instruction Set Extension Fabric (ISEF)

- 32 x 128-bit wide register file

- Aligned load and store

- 8, 16, 32, 64, and 128 bit

- Unaligned load and store

- Up to 16 bytes variable byte streaming I/O

- Up to 32 bits variable bit streaming I/O

- User-defined extensions to the Xtensa ISA

- Defined in C/C++

- Fully pipelined and interlocked

- Support for various operating systems

#### Memory

- 256 KBytes on-chip single-port SRAM

- 32 KBytes instruction cache

- 32 KBytes data cache

- 32 KBytes dual port data SRAM

- Up to 2 GBytes external DDR SDRAM (with ECC)

- DMA controller

#### **Peripherals**

- One PCI/PCI-X port

- Up to four 10/100/1000 Media Access Controllers with bypass to FIFO

- One Serial Peripheral Interface (SPI)

- One Generic Interface Bus (GIB)

Version 1.7 S5610 Data Sheet

- One two-wire interface (TWI)

- Eight General Purpose I/O and interrupt pins (GPIO)

- Two UARTs with IrDA support

- One Standard test port supporting JTAG IEEE 1149.1

- One 64-bit DDR400 SDRAM port with optional error correction code (ECC)

- One 200MHz 64-bit SysAD coprocessor interface

Figure 1 S5610 Block Diagram

\$5610 Data Sheet

Version 1.7

Last modified: 07/12/2006

#### S5610 Features Chapter 1

Stretch's \$5610 software-configurable processors combine the best of two previously divergent semiconductor worlds—the ease of software development associated with general-purpose processors (GPPs) and DSPs, with the parallelism and flexibility of FPGAs. Stretch achieves this by embedding programmable logic entirely inside the processor architecture.

The S5610 processor chip is powered by the Stretch® S5 Engine, which incorporates the widely accepted Tensilica® Xtensa® RISC processor core and the powerful Stretch Instruction Set Extension Fabric (ISEF). The ISEF is a software-configurable data path based on proprietary programmable logic. Using the ISEF, system designers extend the processor instruction set and define the new instructions using only their C/C++ code. As a result, developers get the performance of logic with C/C++ development simplicity—achieving unprecedented performance, easy and rapid development, and significant cost savings.

By integrating a rich set of system and memory peripherals with Stretch's S5 Engine, the S5610 delivers significant cost-performance improvements to a wide range of applications, including:

- Networking

- Telecommunications

- Military

- Security

- Image processing

#### The S5610 Processor 1.1

At the heart of the S5 Engine are a fixed Tensilica Xtensa ISA and Stretch additions to that ISA that allow end-users to add application-specific instructions (Extension Instructions). Tensilica's Xtensa ISA is a RISC architecture designed for embedded applications with industry-leading code density and many modern RISC architectural features. Stretch additions provide a frame-

Version 1.7 S5610 Data Sheet 1-1 work within which Extension Instructions can be specified and implemented to provide significant processing power without requiring the programmer to write in assembly language.

#### 1.1.1 Xtensa ISA

The Xtensa Instruction Set Architecture is a modern RISC ISA targeted at embedded applications. It offers industry-leading code density, and enables high performance and low-power. The Xtensa ISA consists of a rich set of 16- and 24-bit instructions.

Programmers are spared the need to know the details of the Xtensa core architecture, however, because compute-intensive code is optimized using Extension Instructions specified in the C programming language, not in assembly language—a modest familiarity with the Xtensa ISA is all that is really needed.

#### 1.1.2 Stretch Additions

Stretch additions comprise two major components:

- Stretch load-store architecture: This includes a 128-bit wide register file, and a fixed set of instructions supporting a variety of ways to move data efficiently between memory, the Xtensa core register file, and the wide register file.

- Extension Unit: This is a configurable unit for executing Extension Instructions.

Extension Instructions performing complex computations offer several advantages over existing technologies:

- Compared with fixed instruction set architectures, a single Extension

Instruction can, in many cases, replace tens or hundreds of simple instructions.

- Compared with SIMD, VLIW, and Vector architectures, Extension Instructions can accommodate specialized application data sizes as well as specialized computations—providing flexibility previously only available to hardware designs.

- Compared with ASIC and FPGA designs, the Extension Instruction mechanism offers similar flexibility in defining computations without the need to write Verilog or to design complex control logic using finite-state machines. The complex computations are invoked as intrinsics in application software.

- Compared with other products that combine processors with field programmable logic, the S5 architecture enables a completely software-based development methodology using a common set of software development tools.

Version 1.7

1-2

Last modified: 07/12/2006

## 1.2 S5610 Peripherals

The S5610 contains a rich set of peripherals categorized as follows:

- Low-speed peripherals

- Two UART with IrDA ports

- One Serial Peripheral Interface (SPI)

- One two-wire interface (TWI)

- Eight General Purpose I/O and external interrupt pins (GPIO)

- Mid-speed peripherals

- One parallel Generic Interface Bus (GIB) connecting to Flash, SRAM, and Intel- or Motorola-type devices

- Four Programmable Parallel Ports

- FIFO (up to four)

- 10/100/1000 Media Access Controller (up to four)

- High-speed peripherals

- One 64-bit PCI/PCI-X port (32-bit capable)

- One 64-bit DDR400 SDRAM port with optional 32-bit mode, and with optional ECC

- One 64-bit SysAD coprocessor interface

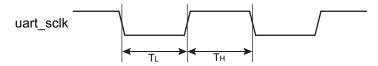

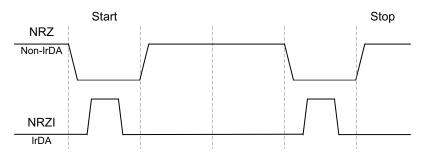

### 1.2.1 UART Ports

The S5610 contains two UART ports that support full duplex, asynchronous, non-DMA transfer of serial data. Each UART supports the following features:

- Completely compatible with the 16550 standard

- Programmable auto flow control mode (for compatibility with the 16750 standard) (UART 0 only)

- 16-byte transmit and receive FIFO depths

- Continuous transmission with low CPU overhead

- IrDA 1.0 SIR (Serial Infrared) mode (115.2 KBaud)

- Fully programmable serial interface

- External 1.8423 MHz clock signal

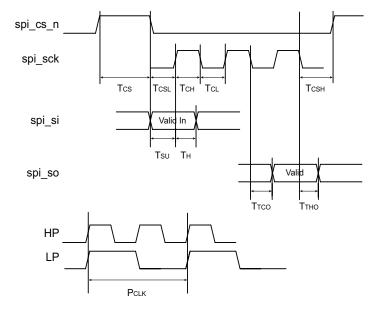

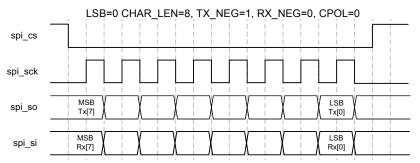

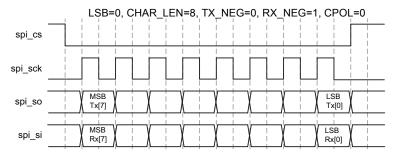

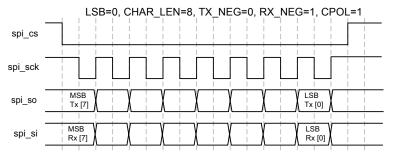

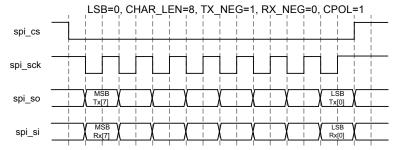

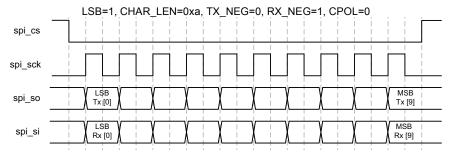

### 1.2.2 Serial Peripheral Interface Port

The Serial Peripheral Interface (SPI) port lets you connect up to eight SPI-compatible slave devices to the S5610. The SPI port supports the following features:

- SPI master operations

- Communication with up to eight devices

- Full duplex synchronous serial data transfer

- Optimized for up to 128-bit transfers (supports longer transfers)

- MSB or LSB data transfer

- Receive and Transfer on rising or falling edge of serial clock (independently)

The SPI device uses three pins for transferring data: two data pins (spi\_si, spi\_so), and a clock pin (spi\_sck). Eight SPI chip select output pins (spi\_cs[7:0]#) lets the S5610 choose up to eight other SPI devices. Using these pins, the SPI port provides a full-duplex, synchronous, master-only serial interface.

### 1.2.3 TWI Interface

The TWI interface lets the S5610 communicate with I2C compatible devices. The TWI is a simple, bi-directional, two-wire, serial data, and serial clock bus for inter-IC control. The interface's features support:

- Both master and slave modes

- Multi-master configurations

- 7-bit addressing

- Both standard and fast modes

Each connected device is recognized by a unique address, and can operate as either a receiver-only device, or as a transmitter with the capability to both receive and send information. Transmitters or receivers can operate in either master or slave mode. The TWI can also be controlled by more than one device connected to it.

The TWI also supports both standard (up to 100 Kb per second) and fast (up to 400 Kb per second) data flow rates.

## 1.2.4 General Purpose I/O Lines

The GPIO supports eight general purpose input-output-interrupt lines.

Version 1.7

1-4

Last modified: 07/12/2006

Software can configure each bit of the GPIO to be either input or output. Each bit may also be controlled individually through addressing registers without affecting adjacent bits. When in input mode, the GPIO can be configured as an interrupt input.

GPIO interrupt capabilities include the ability to:

- Generate an interrupt on any input

- Program inputs independently for level sensitivity (positive or negative) or for edge sensitivity (positive, negative, or both)

- Mask each interrupt individually

- Read the state of an interrupt

- Clear an interrupt

- Generate up to four interrupt outputs from the internal interrupt controller to an external processor

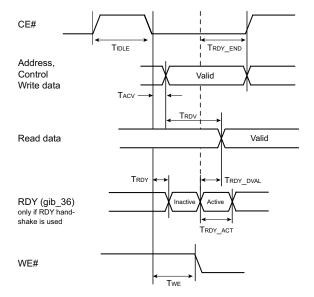

#### 1.2.5 Generic Interface Bus

The S5610 contains a Generic Interface Bus (GIB) designed to support a wide assortment of parallel slave devices. You specify the handshake signals and the timing by writing a short sequence of instructions (typically 3 or fewer), with each instruction specifying the control signals to be activated, and their duration.

The GIB supports the following features:

- Big or little endian devices

- Booting from 16-bit asynchronous Flash memory (28F128J3 or equivalent)

- Most asynchronous 8- or 16-bit Flash memory devices

- Most asynchronous 8- or 16-bit static RAM

- Adjustable timing and programmable handshaking for a wide range of devices

- An external ready signal

- Up to 256 Mbit Flash memories (32 MBytes)

- Support for 32-bit devices

- Support for devices that use multiplexed address-data bus

### 1.2.6 Programmable Parallel Ports

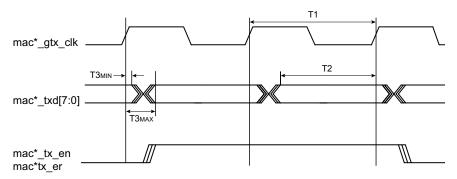

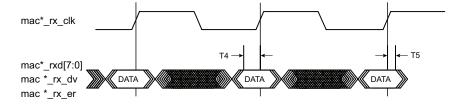

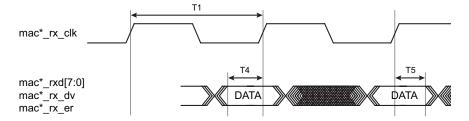

The four independent 8-bit parallel ports are each capable of supporting ethernet traffic or a simple FIFO mode.

- All ports support an IEEE 802.3 compliant GMII and MII interface for 10/100/1000Mbps operation (both full and half-duplex modes)

- Ports 0 and 1 have deeper FIFOs and will therefore provide higher performance than ports 2 and 3 in some applications

- MDIO management interface

- Simple 8-bit FIFO mode for raw data on all ports

- Pairs of ports may be combined to produce a 16-bit FIFO mode for raw data

#### 1.2.7 PCI-X Interface

The PCI-X core module provides access to the S5610 from any PCI or PCI-X bus initiator or target. It can also be configured as a host bridge. The PCI-X controller supports the following features:

- Compliance with PCI Bus Revision 2.3, and with PCI-X Addendum Revision 1.0a

- 32- or 64-bit PCI or PCI-X interface

- Synchronous 22.22–133 MHz PCI-X-to-application clock frequencies

- Support for

- PCI-X Timing A Decode and PCI Medium Decode

- Master Deferred (up to 2) and Target Delayed (up to 8) Read transactions

- Master (up to 8) and Target (up to 16) Split Read-Write transactions

- PCI Target Fast Back-to-Back Cycle

- Memory word address for Control Register access

- PCI-X Bus Message Signaled Interrupt

- Various clock and data width configurations

- Application or Configuration Register-requested Target

- Abort-Retry cycles, Deferred Read transactions, and Split Read–Write transactions

- PCI Target Burst size of up to 2 MBytes, aligned

- PCI-X Target Burst size of up to 256 KBytes

- PCI and PCI-X Master Burst size of up to 256 bytes per access

- Application Interface Configuration Register access port

### 1.2.8 SysAD Interface

The SysAD bus interface allows the S5610 to be a slave coprocessor and DDR controller. Its features include:

1+ GBytes per second bandwidth—64-bits at up to 200 MHz (HSTL)

Version 1.7

1-6

Last modified: 07/12/2006

- Support for single and burst access from the CPU

- Multiplexed address–data bus

- 36 bits of physical address (translated to an internal 32-bit address)

- 64 bits of data

- Support for two outstanding reads, which can be returned out of order

- Boot available from the SysAD bus when the connected chip includes a boot bus that connects to Flash or ROM memory

#### 1.2.9 DDR Controller

The S5610 DDR SDRAM controller interfaces to the various available SDRAM DDR400 and lower devices. It supports the following features:

- Fully pipelined command, read, and write data interface

- Advanced bank lookahead for high memory throughput

- Programmable register interface to control memory device parameters and protocols such as auto-precharge

- Built-in adjustable Delay Compensation Circuitry for reliable data transmit and receive timing

- Error correction code (ECC) functionality for single bit correction, and double bit error detection circuitry with programmable detection and correction of ECC events (64-bit mode only)

- Clock frequencies from 100 MHz to 200 MHz

#### 1.2.10 JTAG

S5610 processor chips contain one JTAG test access port. This port is used as a portal into the chip for booting, on-chip debugging (OCD), testing, and boundary scanning functions.

### 1.2.10.1 On Chip Debugging

OCD allows access to the processor subsystem through the JTAG port. This permits a debug probe to be plugged into the JTAG port to single-step, modify memory and registers, and to provide hardware breakpoints and watchpoints.

Setting the debug pin determines whether JTAG or OCD mode is selected; when set to 0, JTAG is selected; when set to 1, OCD is selected. Refer to "GIB Bootstrapping Options" on page 3-12 for more information on bootstrapping options.

### 1.3 Clocks

The S5610 contains five phase locked loops (PLLs). PLL1 generates the DDR clock and, optionally, the PCI and Programmable Parallel port clocks. PLL2 generates the clocks for the core logic, including the processor. The remaining three PLLs are used for clock de-skew for the PCI, DDR, and SysAD interfaces.

Clock pins are provided for PLL1 and PLL2, and for the various interfaces.

### 1.4 Reset

The S5610 contains numerous internal resets, mostly derived from one master reset supplied externally. All global resets are generated in a single reset block. All generated resets are synchronous to a specific block, depending on the reset destination.

The three modes recognized by the reset block are: power-on, hard reset, and soft reset.

- Power-on Reset: This mode is active while the chip is powering up, and is equivalent to a hard reset. Reset is released to the PLLs after power-up, based on board-level power-up reset circuitry.

- Hard Reset: This mode resets everything on the chip, and is a result of asserting the global reset.

- Soft Reset: This reset is initiated by a software action, PCI reset (when in PCI slave mode), or by a watchdog reset non-maskable interrupt. The processor, bus, all peripherals, and most of the system registers blocks are reset by a soft reset, except for the PLLs.

### 1.5 Interrupt Controller

Each I/O device on the S5610 can generate a set of interrupts to the Xtensa core. The interrupt controller allows each interrupt source to be mapped to any of the Xtensa core's 20 interrupt inputs. This permits flexible software-controlled mapping of interrupts into distinct priority groups.

Version 1.7

1-8

Last modified: 07/12/2006

A total of 20 interrupts, one of which is an NMI, are provided. Of these 20 interrupts, four can be output through the GPIO to an external processor. An additional interrupt output is provided to the PCI block to allow generation of a PCI interrupt.

The interrupt controller supports the following features:

- Interrupts can be enabled or disabled

- Any interrupt source (input) can activate any single interrupt output, including NMI, and each source controls its own cause and clear mechanism

- Any interrupt output can be activated by any number of interrupt inputs

- A status register shows which interrupt inputs are active *and* unmasked

- An aggregation register shows status based upon blocks of interrupts

- Synchronizers are present on all interrupt inputs

- Up to four external interrupts can originate through the GPIO

- The edge trigger programming for the external interrupts is done in the GPIO controller

## 1.6 Memory Architecture

Stretch's memory architecture supports the following features:

- 32 KB instruction cache (4-way associative, with parity)

- 32 KB data cache (2-way associative, with parity)

- Support for write-back cache and write-through cache

- 32 KB dual-port local data memory, with parity

- 256 KB on-chip SRAM, with parity

- Up to 2 GB of 64-bit wide DDR400 (up to 1 GB of 32-bit)

- Operation from internal SRAM without DDR

### 1.7 DMA Controller

The DMA Controller (DMAC) provides four master interfaces for implementing DMA transfers between system memory (SRAM and DRAM) and various peripherals. A slave interface is also provided for configuring and monitoring DMA operations.

Dual Inst. Data SRAM SRAM Port SRAM **Xtensa** Reg File **ISEF** SysAD < DMA Port 0 Port 1 Port 2 DDR **Memory Controller** SDRAM

Figure 1-1 S5610 memory block diagram

The DMA Controller supports 24 unidirectional DMA channels, where each channel has a programmable priority (0-3) and a dedicated peripheral interface. An internal transfer buffer and logic support both single- and dual-master transfers that utilize the full bus bandwidth. Per-channel scatter—gather operations are also supported.

Software overhead to manage network peripherals is minimized through the following features:

- A descriptor-based control scheme to queue, process, and monitor transfers.

- Pre- or post-fix operations per transfer that allow the DMAC to interact autonomously with peripherals without per-packet software intervention.

- Programmable interrupts.

S5610 Data Sheet

Version 1.7

1-10

Last modified: 07/12/2006

SRAM/

Dual-Port Data RAM

DDR

DDR

DMA

ISEF

Controller

Programmable Parallel Ports GIB

PCI

Configuration

Controller

Figure 1-2 DMA controller block diagram

Version 1.7

1-12

Last modified: 07/12/2006

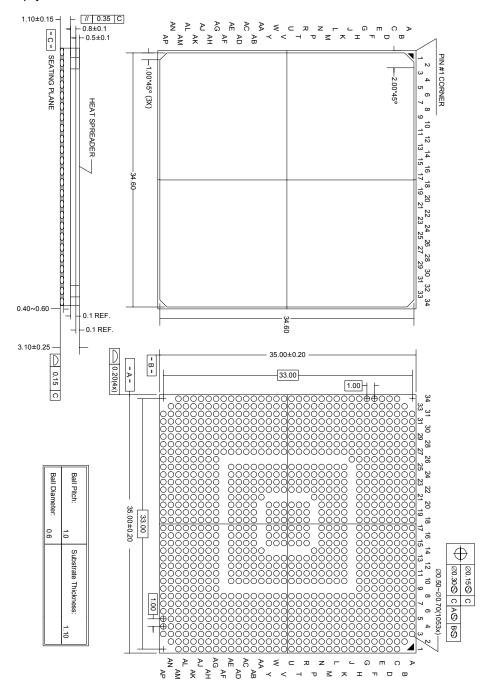

# Chapter 2 The S5610 Package

The S5610 package is a 35 mm x 35 mm Flip-Chip BGA with a heat spreader (HFCBGA). Table 2-1 lists signal-to-pin mappings as well as a short description for all signals except those for the coprocessor interface (SysAD, see Table 2-2) and the Programmable Parallel Interface (PPI, refer to Section 2.1, "Programmable Port Interface").

Table 2-1 S5610 Signal Description (alphabetic within ports)

| Port | Signal Name    | Pin # | Type | Description                     |

|------|----------------|-------|------|---------------------------------|

| DDR  | sdram_addr[0]  | D20   | 0    | Address to DDR memories         |

|      | sdram_addr[1]  | E17   | 0    | Address to DDR memories         |

|      | sdram_addr[2]  | D17   | 0    | Address to DDR memories         |

|      | sdram_addr[3]  | D16   | 0    | Address to DDR memories         |

|      | sdram_addr[4]  | E15   | 0    | Address to DDR memories         |

|      | sdram_addr[5]  | E14   | 0    | Address to DDR memories         |

|      | sdram_addr[6]  | D15   | 0    | Address to DDR memories         |

|      | sdram_addr[7]  | D13   | 0    | Address to DDR memories         |

|      | sdram_addr[8]  | E13   | 0    | Address to DDR memories         |

|      | sdram_addr[9]  | D12   | 0    | Address to DDR memories         |

|      | sdram_addr[10] | E20   | 0    | Address to DDR memories         |

|      | sdram_addr[11] | E11   | 0    | Address to DDR memories         |

|      | sdram_addr[12] | E10   | 0    | Address to DDR memories         |

|      | sdram_addr[13] | D6    | 0    | Address to DDR memories         |

|      | sdram_bank[0]  | E21   | 0    | Bank address to memory          |

|      | sdram_bank[1]  | D21   | 0    | Bank address to memory          |

|      | sdram_cas#     | E24   | 0    | Column address strobe           |

|      | sdram_ck[0]    | E29   | 0    | Clock to DDR memories           |

|      | sdram_ck[1]    | D19   | 0    | Clock to DDR memories           |

|      | sdram_ck[2]    | D7    | 0    | Clock to DDR memories           |

|      | sdram_ck[0]#   | D29   | 0    | Clock to DDR memories, inverted |

|      | sdram_ck[1]#   | E19   | 0    | Clock to DDR memories, inverted |

|      | sdram_ck[2]#   | E7    | 0    | Clock to DDR memories, inverted |

|      |                |       |      |                                 |

Table 2-1 S5610 Signal Description (alphabetic within ports)

| Port        | Signal Name  | Pin # | Type | Description                                                |

|-------------|--------------|-------|------|------------------------------------------------------------|

| DDR (cont.) | sdram_cke0   | D8    | 0    | Clock enable                                               |

|             | sdram_ckel   | D9    | 0    | Clock enable                                               |

|             | sdram_clk_fb | B33   | I    | Feedback clock for the SDRAM deskew PLL                    |

|             | sdram_cs[0]# | D24   | 0    | Chip select                                                |

|             | sdram_cs[1]# | E25   | 0    | Chip select                                                |

|             | sdram_cs[2]# | E26   | 0    | Chip select                                                |

|             | sdram_cs[3]# | D27   | 0    | Chip select                                                |

|             | sdram_dm[0]  | C4    | 0    | Data mask. When active, inhibits writing the selected byte |

|             | sdram_dm[1]  | A8    | 0    | Data mask. When active, inhibits writing the selected byte |

|             | sdram_dm[2]  | B11   | 0    | Data mask. When active, inhibits writing the selected byte |

|             | sdram_dm[3]  | C14   | 0    | Data mask. When active, inhibits writing the selected byte |

|             | sdram_dm[4]  | C21   | 0    | Data mask. When active, inhibits writing the selected byte |

|             | sdram_dm[5]  | C24   | 0    | Data mask. When active, inhibits writing the selected byte |

|             | sdram_dm[6]  | C27   | 0    | Data mask. When active, inhibits writing the selected byte |

|             | sdram_dm[7]  | A31   | 0    | Data mask. When active, inhibits writing the selected byte |

|             | sdram_dq[0]  | В3    | I/O  | Data. Output during writes; input during reads             |

|             | sdram_dq[1]  | Α4    | I/O  | Data. Output during writes; input during reads             |

|             | sdram_dq[2]  | A5    | I/O  | Data. Output during writes; input during reads             |

|             | sdram_dq[3]  | Α6    | I/O  | Data. Output during writes; input during reads             |

|             | sdram_dq[4]  | А3    | I/O  | Data. Output during writes; input during reads             |

|             | sdram_dq[5]  | C3    | I/O  | Data. Output during writes; input during reads             |

|             | sdram_dq[6]  | B5    | I/O  | Data. Output during writes; input during reads             |

|             | sdram_dq[7]  | C5    | I/O  | Data. Output during writes; input during reads             |

|             | sdram_dq[8]  | В6    | I/O  | Data. Output during writes; input during reads             |

|             | sdram_dq[9]  | C6    | I/O  | Data. Output during writes; input during reads             |

|             | sdram_dq[10] | Α9    | I/O  | Data. Output during writes; input during reads             |

|             | sdram_dq[11] | В9    | I/O  | Data. Output during writes; input during reads             |

|             | sdram_dq[12] | A7    | I/O  | Data. Output during writes; input during reads             |

|             | sdram_dq[13] | C7    | I/O  | Data. Output during writes; input during reads             |

|             | sdram_dq[14] | B8    | I/O  | Data. Output during writes; input during reads             |

|             | sdram_dq[15] | C8    | I/O  | Data. Output during writes; input during reads             |

|             | sdram_dq[16] | A10   | I/O  | Data. Output during writes; input during reads             |

|             | sdram_dq[17] | B10   | I/O  | Data. Output during writes; input during reads             |

|             | sdram_dq[18] | C11   | I/O  | Data. Output during writes; input during reads             |

|             |              |       |      |                                                            |

Version 1.7

2-2

Last modified: 07/12/2006

Table 2-1 S5610 Signal Description (alphabetic within ports)

| Port        | Signal Name  | Pin # | Type | Description                                    |

|-------------|--------------|-------|------|------------------------------------------------|

| DDR (cont.) | sdram_dq[19] | B12   | I/O  | Data. Output during writes; input during reads |

|             | sdram_dq[20] | C9    | I/O  | Data. Output during writes; input during reads |

|             | sdram_dq[21] | A11   | I/O  | Data. Output during writes; input during reads |

|             | sdram_dq[22] | A12   | I/O  | Data. Output during writes; input during reads |

|             | sdram_dq[23] | C12   | I/O  | Data. Output during writes; input during reads |

|             | sdram_dq[24] | A13   | I/O  | Data. Output during writes; input during reads |

|             | sdram_dq[25] | C13   | I/O  | Data. Output during writes; input during reads |

|             | sdram_dq[26] | A15   | I/O  | Data. Output during writes; input during reads |

|             | sdram_dq[27] | C15   | I/O  | Data. Output during writes; input during reads |

|             | sdram_dq[28] | B13   | I/O  | Data. Output during writes; input during reads |

|             | sdram_dq[29] | A14   | I/O  | Data. Output during writes; input during reads |

|             | sdram_dq[30] | B15   | I/O  | Data. Output during writes; input during reads |

|             | sdram_dq[31] | A16   | I/O  | Data. Output during writes; input during reads |

|             | sdram_dq[32] | C19   | I/O  | Data. Output during writes; input during reads |

|             | sdram_dq[33] | B20   | I/O  | Data. Output during writes; input during reads |

|             | sdram_dq[34] | B21   | I/O  | Data. Output during writes; input during reads |

|             | sdram_dq[35] | C22   | I/O  | Data. Output during writes; input during reads |

|             | sdram_dq[36] | A20   | I/O  | Data. Output during writes; input during reads |

|             | sdram_dq[37] | C20   | I/O  | Data. Output during writes; input during reads |

|             | sdram_dq[38] | A22   | I/O  | Data. Output during writes; input during reads |

|             | sdram_dq[39] | B22   | I/O  | Data. Output during writes; input during reads |

|             | sdram_dq[40] | A23   | I/O  | Data. Output during writes; input during reads |

|             | sdram_dq[41] | A24   | I/O  | Data. Output during writes; input during reads |

|             | sdram_dq[42] | A25   | I/O  | Data. Output during writes; input during reads |

|             | sdram_dq[43] | B25   | I/O  | Data. Output during writes; input during reads |

|             | sdram_dq[44] | B23   | I/O  | Data. Output during writes; input during reads |

|             | sdram_dq[45] | C23   | I/O  | Data. Output during writes; input during reads |

|             | sdram_dq[46] | C25   | I/O  | Data. Output during writes; input during reads |

|             | sdram_dq[47] | A26   | I/O  | Data. Output during writes; input during reads |

|             | sdram_dq[48] | B26   | I/O  | Data. Output during writes; input during reads |

|             | sdram_dq[49] | A27   | I/O  | Data. Output during writes; input during reads |

|             | sdram_dq[50] | A29   | I/O  | Data. Output during writes; input during reads |

|             | sdram_dq[51] | B29   | I/0  | Data. Output during writes; input during reads |

|             | sdram_dq[52] | C26   | I/O  | Data. Output during writes; input during reads |

|             |              |       |      |                                                |

Table 2-1 S5610 Signal Description (alphabetic within ports)

| Port        | Signal Name     | Pin # | Туре | Description                                                                                             |

|-------------|-----------------|-------|------|---------------------------------------------------------------------------------------------------------|

| DDR (cont.) | sdram_dq[53]    | B27   | I/O  | Data. Output during writes; input during reads                                                          |

|             | sdram_dq[54]    | B28   | I/0  | Data. Output during writes; input during reads                                                          |

|             | sdram_dq[55]    | C28   | I/O  | Data. Output during writes; input during reads                                                          |

|             | sdram_dq[56]    | B30   | I/0  | Data. Output during writes; input during reads                                                          |

|             | sdram_dq[57]    | C30   | I/O  | Data. Output during writes; input during reads                                                          |

|             | sdram_dq[58]    | B32   | I/O  | Data. Output during writes; input during reads                                                          |

|             | sdram_dq[59]    | C32   | I/O  | Data. Output during writes; input during reads                                                          |

|             | sdram_dq[60]    | C29   | I/O  | Data. Output during writes; input during reads                                                          |

|             | sdram_dq[61]    | A30   | I/O  | Data. Output during writes; input during reads                                                          |

|             | sdram_dq[62]    | C31   | I/O  | Data. Output during writes; input during reads                                                          |

|             | sdram_dq[63]    | A32   | I/O  | Data. Output during writes; input during reads                                                          |

|             | sdram_dqs[0]    | В4    | I/O  | Data strobe. Output during writes; input during reads                                                   |

|             | sdram_dqs[1]    | В7    | I/O  | Data strobe. Output during writes; input during reads                                                   |

|             | sdram_dqs[2]    | C10   | I/O  | Data strobe. Output during writes; input during reads                                                   |

|             | sdram_dqs[3]    | B14   | I/O  | Data strobe. Output during writes; input during reads                                                   |

|             | sdram_dqs[4]    | A21   | I/O  | Data strobe. Output during writes; input during reads                                                   |

|             | sdram_dqs[5]    | B24   | I/O  | Data strobe. Output during writes; input during reads                                                   |

|             | sdram_dqs[6]    | A28   | I/O  | Data strobe. Output during writes; input during reads                                                   |

|             | sdram_dqs[7]    | B31   | I/O  | Data strobe. Output during writes; input during reads                                                   |

|             | sdram_ecc_dm    | A18   | I/0  | ECC data. Output during writes; input during reads If unused, this pin should terminate with a pull-up. |

|             | sdram_ecc_dq[0] | A17   | I/0  | ECC data. Output during writes; input during reads If unused, this pin should terminate with a pull-up. |

|             | sdram_ecc_dq[1] | B17   | I/0  | ECC data. Output during writes; input during reads If unused, this pin should terminate with a pull-up. |

|             | sdram_ecc_dq[2] | B18   | I/0  | ECC data. Output during writes; input during reads If unused, this pin should terminate with a pull-up. |

|             | sdram_ecc_dq[3] | A19   | I/0  | ECC data. Output during writes; input during reads If unused, this pin should terminate with a pull-up. |

|             | sdram_ecc_dq[4] | B16   | I/0  | ECC data. Output during writes; input during reads If unused, this pin should terminate with a pull-up. |

|             | sdram_ecc_dq[5] | C16   | I/0  | ECC data. Output during writes; input during reads If unused, this pin should terminate with a pull-up. |

|             | sdram_ecc_dq[6] | C18   | I/0  | ECC data. Output during writes; input during reads If unused, this pin should terminate with a pull-up. |

|             | sdram_ecc_dq[7] | B19   | I/O  | ECC data. Output during writes; input during reads If unused, this pin should terminate with a pull-up. |

|             |                 |       |      |                                                                                                         |

Version 1.7

2-4

Last modified: 07/12/2006

Table 2-1 S5610 Signal Description (alphabetic within ports)

| Port        | Signal Name     | Pin # | Type | Description                                                                                               |

|-------------|-----------------|-------|------|-----------------------------------------------------------------------------------------------------------|

| DDR (cont.) | sdram_ecc_dqs   | C17   | I/O  | ECC strobe. Output during writes; input during reads If unused, this pin should terminate with a pull-up. |

|             | sdram_ras#      | E22   | 0    | Row address strobe                                                                                        |

|             | sdram_sel_ddr32 | D30   | I    | Selects memory width. Set high it selects 32-bit plus ECC. Set low it selects 64-bit plus ECC.            |

|             | sdram_we#       | D23   | 0    | Write enable                                                                                              |

|             | sstl_ref1       | D25   | I    | Reference voltage for the SDRAM interface                                                                 |

|             | sstl_ref2       | D11   | I    | Reference voltage for the SDRAM interface                                                                 |

| GIB         | gib[0]          | AM1   | I/O  | General purpose address and data<br>This signal has an internal pull-up resistor of nominally 10K ohms.   |

|             | gib[1]          | AM2   | I/O  | General purpose address and data<br>This signal has an internal pull-up resistor of nominally 10K ohms.   |

|             | gib[2]          | AN2   | I/O  | General purpose address and data<br>This signal has an internal pull-up resistor of nominally 10K ohms.   |

|             | gib[3]          | AL3   | I/0  | General purpose address and data<br>This signal has an internal pull-up resistor of nominally 10K ohms.   |

|             | gib[4]          | AL4   | I/0  | General purpose address and data<br>This signal has an internal pull-up resistor of nominally 10K ohms.   |

|             | gib[5]          | AM3   | I/0  | General purpose address and data<br>This signal has an internal pull-up resistor of nominally 10K ohms.   |

|             | gib[6]          | AK5   | I/0  | General purpose address and data<br>This signal has an internal pull-up resistor of nominally 10K ohms.   |

|             | gib[7]          | AL1   | I/0  | General purpose address and data<br>This signal has an internal pull-up resistor of nominally 10K ohms.   |

|             | gib[8]          | AL2   | I/0  | General purpose address and data<br>This signal has an internal pull-up resistor of nominally 10K ohms.   |

|             | gib[9]          | AK4   | I/0  | General purpose address and data<br>This signal has an internal pull-up resistor of nominally 10K ohms.   |

|             | gib[10]         | AK2   | I/O  | General purpose address and data<br>This signal has an internal pull-up resistor of nominally 10K ohms.   |

|             | gib[11]         | AK1   | I/0  | General purpose address and data<br>This signal has an internal pull-up resistor of nominally 10K ohms.   |

|             | gib[12]         | AK3   | I/O  | General purpose address and data<br>This signal has an internal pull-up resistor of nominally 10K ohms.   |

|             | gib[13]         | AH7   | I/0  | General purpose address and data<br>This signal has an internal pull-up resistor of nominally 10K ohms.   |

|             | gib[14]         | AJ5   | I/O  | General purpose address and data<br>This signal has an internal pull-up resistor of nominally 10K ohms.   |

|             | gib[15]         | AJ6   | I/0  | General purpose address and data<br>This signal has an internal pull-up resistor of nominally 10K ohms.   |

|             |                 |       |      |                                                                                                           |

Table 2-1 S5610 Signal Description (alphabetic within ports)

| Port        | Signal Name | Pin # | Type | Description                                                                                                                                                                                                                                     |

|-------------|-------------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GIB (cont.) | gib[16]     | AH6   | I/O  | General purpose address and data<br>This signal has an internal pull-up resistor of nominally 10K ohms.                                                                                                                                         |

|             | gib[17]     | AJ2   | I/0  | General purpose address and data<br>This signal has an internal pull-up resistor of nominally 10K ohms.                                                                                                                                         |

|             | gib[18]     | AJ3   | I/O  | General purpose address and data<br>This signal has an internal pull-up resistor of nominally 10K ohms.                                                                                                                                         |

|             | gib[19]     | AJ4   | I/0  | General purpose address and data<br>This signal has an internal pull-up resistor of nominally 10K ohms.                                                                                                                                         |

|             | gib[20]     | AJ1   | I/0  | General purpose address and data<br>This signal has an internal pull-up resistor of nominally 10K ohms.                                                                                                                                         |

|             | gib[21]     | AH2   | I/0  | General purpose address and data<br>This signal has an internal pull-up resistor of nominally 10K ohms.                                                                                                                                         |

|             | gib[22]     | АН3   | I/O  | General purpose address and data<br>This signal has an internal pull-up resistor of nominally 10K ohms.                                                                                                                                         |

|             | gib[23]     | AH4   | I/O  | General purpose address and data<br>This signal has an internal pull-up resistor of nominally 10K ohms.                                                                                                                                         |

|             | gib[24]     | AH1   | I/0  | General purpose address and data<br>This signal has an internal pull-up resistor of nominally 10K ohms.                                                                                                                                         |

|             | gib[25]     | AF7   | I/O  | General purpose address and data.<br>This signal has an internal pull-up resistor of nominally 10K ohms.                                                                                                                                        |

|             | gib[26]     | AG5   | I/0  | General purpose address and data.<br>This signal has an internal pull-up resistor of nominally 10K ohms.                                                                                                                                        |

|             | gib[27]     | AG6   | I/0  | General purpose address and data.<br>This signal has an internal pull-up resistor of nominally 10K ohms.                                                                                                                                        |

|             | gib[28]     | AF6   | I/0  | General purpose address and data.<br>This signal has an internal pull-up resistor of nominally 10K ohms.                                                                                                                                        |

|             | gib[29]     | AG2   | I/0  | General purpose address and data.<br>This signal has an internal pull-up resistor of nominally 10K ohms.                                                                                                                                        |

|             | gib[30]     | AG3   | I/O  | General purpose address and data.<br>This signal has an internal pull-up resistor of nominally 10K ohms.                                                                                                                                        |

|             | gib[31]     | AG4   | I/0  | General purpose address and data.<br>This signal has an internal pull-up resistor of nominally 10K ohms.                                                                                                                                        |

|             | gib[32]     | AF3   | I/O  | General purpose control or address out. During reset, this pin is hclk_sel[0] input, which controls pll2 operation. Refer to Section 3.6.11, "PLL and Clock Timing" and Table 3-31 for the relationship between this pin and the PLL operation. |

|             | gib[33]     | AF4   | I/O  | General purpose control or address out. During reset, this pin is hclk_sel[1] input, which controls pll2 operation. Refer to Section 3.6.11, "PLL and Clock Timing" and Table 3-31 for the relationship between this pin and the PLL operation. |

Version 1.7

2-6

Last modified: 07/12/2006

Table 2-1 S5610 Signal Description (alphabetic within ports)

| Port        | Signal Name | Pin # | Туре | Description                                                                                                                                                                                                                                     |

|-------------|-------------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GIB (cont.) | gib[34]     | AG1   | I/O  | General purpose control or address out. During reset, this pin is hclk_sel[2] input, which controls pll2 operation. Refer to Section 3.6.11, "PLL and Clock Timing" and Table 3-31 for the relationship between this pin and the PLL operation. |

|             | gib[35]     | AF2   | I/O  | General purpose control or address out. During reset, this pin is pci_host_mode in.                                                                                                                                                             |

|             | gib[36]     | AE5   | I/O  | General purpose control or address out, or ready in.<br>This signal has an internal pull-up resistor of nominally 10K ohms.                                                                                                                     |

|             | gib[37]     | AE6   | I/O  | General purpose control or address out. During reset, this is flash_enable#.                                                                                                                                                                    |

|             | gib[38]     | AF1   | 0    | General purpose control or address out                                                                                                                                                                                                          |

|             | gib[39]     | AE4   | 0    | General purpose control or address out                                                                                                                                                                                                          |

|             | gib[40]     | AE1   | 0    | General purpose control out                                                                                                                                                                                                                     |

|             | gib[41]     | AE2   | 0    | General purpose control out                                                                                                                                                                                                                     |

|             | gib_ce[0]#  | AE3   | 0    | Active low chip enables to external devices                                                                                                                                                                                                     |

|             | gib_ce[1]#  | AD7   | 0    | Active low chip enables to external devices                                                                                                                                                                                                     |

|             | gib_ce[2]#  | AD3   | 0    | Active low chip enables to external devices                                                                                                                                                                                                     |

|             | gib_ce[3]#  | AD4   | 0    | Active low chip enables to external devices                                                                                                                                                                                                     |

| GPI0        | gpio[0]     | AF32  | I/O  | General purpose I/O signals mapped to register space                                                                                                                                                                                            |

|             | gpio[1]     | AE29  | I/O  | General purpose I/O signals mapped to register space                                                                                                                                                                                            |

|             | gpio[2]     | AF34  | I/O  | General purpose I/O signals mapped to register space                                                                                                                                                                                            |

|             | gpio[3]     | AF33  | I/O  | General purpose I/O signals mapped to register space                                                                                                                                                                                            |

|             | gpio[4]     | AG32  | I/O  | General purpose I/O signals mapped to register space                                                                                                                                                                                            |

|             | gpio[5]     | AF31  | I/O  | General purpose I/O signals mapped to register space                                                                                                                                                                                            |

|             | gpio[6]     | AG34  | I/O  | General purpose I/O signals mapped to register space                                                                                                                                                                                            |

|             | gpio[7]     | AG33  | I/O  | General purpose I/O signals mapped to register space                                                                                                                                                                                            |

| JTAG        | tck         | AK34  | I    | JTAG (IEEE 1149.1) clock input.<br>This signal has an internal pull-down resistor of nominally 10K ohms.<br>If this feature is not being used, do not connect to this pin.                                                                      |

|             | tdi         | AK33  | I    | JTAG (IEEE 1149.1) serial data in.<br>This signal has an internal pull-up resistor of nominally 10K ohms.<br>If this feature is not being used, do not connect to this pin.                                                                     |

|             | tdo         | AJ31  | 0    | JTAG (IEEE 1149.1) serial data out.<br>If this feature is not being used, do not connect to this pin.                                                                                                                                           |

|             | tms         | AJ29  | I    | JTAG (IEEE 1149.1) tap mode select in.<br>This signal has an internal pull-up resistor of nominally 10K ohms.<br>If this feature is not being used, do not connect to this pin.                                                                 |

|             |             |       |      |                                                                                                                                                                                                                                                 |

Table 2-1 S5610 Signal Description (alphabetic within ports)

| Port         | Signal Name | Pin # | Туре | Description                                                                                                                                                                |

|--------------|-------------|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JTAG (cont.) | trst#       | AJ30  | I    | JTAG (IEEE 1149.1) reset in. This signal has an internal pull-up resistor of nominally 10K ohms. If the JTAG port is not being used, drive this pin low or connect to Vss. |

| PCI          | pci_ack64#  | N32   | I/O  | Accept 64-bit transfer                                                                                                                                                     |

|              | pci_ad[0]   | R31   | I/O  | Address-data                                                                                                                                                               |

|              | pci_ad[1]   | N33   | I/O  | Address-data                                                                                                                                                               |

|              | pci_ad[2]   | T28   | I/O  | Address-data                                                                                                                                                               |

|              | pci_ad[3]   | N34   | I/O  | Address-data                                                                                                                                                               |

|              | pci_ad[4]   | T29   | I/O  | Address-data                                                                                                                                                               |

|              | pci_ad[5]   | P32   | I/O  | Address-data                                                                                                                                                               |

|              | pci_ad[6]   | T31   | I/O  | Address-data                                                                                                                                                               |

|              | pci_ad[7]   | P33   | I/O  | Address-data                                                                                                                                                               |

|              | pci_ad[8]   | P34   | I/O  | Address-data                                                                                                                                                               |

|              | pci_ad[9]   | U30   | I/O  | Address-data                                                                                                                                                               |

|              | pci_ad[10]  | R33   | I/O  | Address-data                                                                                                                                                               |

|              | pci_ad[11]  | U31   | I/O  | Address-data                                                                                                                                                               |

|              | pci_ad[12]  | R34   | I/O  | Address-data                                                                                                                                                               |

|              | pci_ad[13]  | V28   | I/O  | Address-data                                                                                                                                                               |

|              | pci_ad[14]  | T32   | I/O  | Address-data                                                                                                                                                               |

|              | pci_ad[15]  | V29   | I/O  | Address-data                                                                                                                                                               |

|              | pci_ad[16]  | Y28   | I/O  | Address-data                                                                                                                                                               |

|              | pci_ad[17]  | V34   | I/O  | Address-data                                                                                                                                                               |

|              | pci_ad[18]  | Y29   | I/O  | Address-data                                                                                                                                                               |

|              | pci_ad[19]  | W32   | I/O  | Address-data                                                                                                                                                               |

|              | pci_ad[20]  | Y31   | I/O  | Address-data                                                                                                                                                               |

|              | pci_ad[21]  | W33   | I/O  | Address-data                                                                                                                                                               |

|              | pci_ad[22]  | AA29  | I/O  | Address-data                                                                                                                                                               |

|              | pci_ad[23]  | W34   | I/O  | Address-data                                                                                                                                                               |

|              | pci_ad[24]  | AA31  | I/O  | Address-data                                                                                                                                                               |

|              | pci_ad[25]  | Y33   | I/O  | Address-data                                                                                                                                                               |

|              | pci_ad[26]  | AB28  | I/O  | Address–data                                                                                                                                                               |

|              | pci_ad[27]  | Y34   | I/O  | Address-data                                                                                                                                                               |

|              | pci_ad[28]  | AB29  | I/O  | Address-data                                                                                                                                                               |

|              | pci_ad[29]  | AA32  | I/O  | Address-data                                                                                                                                                               |

|              |             |       |      |                                                                                                                                                                            |

Version 1.7

2-8

Last modified: 07/12/2006

Table 2-1 S5610 Signal Description (alphabetic within ports)

| Port        | Signal Name | Pin # | Туре | Description  |

|-------------|-------------|-------|------|--------------|

| PCI (cont.) | pci_ad[30]  | AB31  | I/O  | Address-data |

|             | pci_ad[31]  | AA33  | I/O  | Address-data |

|             | pci_ad[32]  | J29   | I/O  | Address-data |

|             | pci_ad[33]  | G32   | I/O  | Address-data |

|             | pci_ad[34]  | J30   | I/O  | Address-data |

|             | pci_ad[35]  | G33   | I/O  | Address-data |

|             | pci_ad[36]  | J31   | I/O  | Address-data |

|             | pci_ad[37]  | G34   | I/O  | Address-data |

|             | pci_ad[38]  | K28   | I/O  | Address-data |

|             | pci_ad[39]  | H32   | I/O  | Address-data |

|             | pci_ad[40]  | K29   | I/O  | Address-data |

|             | pci_ad[41]  | H33   | I/O  | Address-data |

|             | pci_ad[42]  | K31   | I/O  | Address-data |

|             | pci_ad[43]  | H34   | I/O  | Address-data |

|             | pci_ad[44]  | L29   | I/O  | Address-data |

|             | pci_ad[45]  | J32   | I/O  | Address-data |

|             | pci_ad[46]  | L30   | I/O  | Address-data |

|             | pci_ad[47]  | J33   | I/O  | Address-data |

|             | pci_ad[48]  | L31   | I/O  | Address-data |

|             | pci_ad[49]  | J34   | I/O  | Address-data |

|             | pci_ad[50]  | M28   | I/O  | Address-data |

|             | pci_ad[51]  | K32   | I/O  | Address-data |

|             | pci_ad[52]  | M29   | I/O  | Address-data |

|             | pci_ad[53]  | K33   | I/O  | Address-data |

|             | pci_ad[54]  | M31   | I/O  | Address-data |

|             | pci_ad[55]  | K34   | I/O  | Address-data |

|             | pci_ad[56]  | N29   | I/O  | Address-data |

|             | pci_ad[57]  | L32   | I/O  | Address-data |

|             | pci_ad[58]  | N30   | I/O  | Address-data |

|             | pci_ad[59]  | L33   | I/0  | Address-data |

|             | pci_ad[60]  | N31   | I/O  | Address-data |

|             | pci_ad[61]  | L34   | I/0  | Address-data |

|             | pci_ad[62]  | P28   | I/O  | Address-data |

|             | pci_ad[63]  | M32   | I/O  | Address-data |

|             |             |       |      |              |

Table 2-1 S5610 Signal Description (alphabetic within ports)

| Port        | Signal Name    | Pin # | Туре | Description                                                                                                                                                                                                                    |

|-------------|----------------|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCI (cont.) | pci_cbe[0]#    | U29   | I/O  | Command and byte enables                                                                                                                                                                                                       |

|             | pci_cbe[1]#    | T33   | I/O  | Command and byte enables                                                                                                                                                                                                       |

|             | pci_cbe[2]#    | V33   | I/O  | Command and byte enables                                                                                                                                                                                                       |

|             | pci_cbe[3]#    | Y32   | I/O  | Command and byte enables                                                                                                                                                                                                       |

|             | pci_cbe[4]#    | M33   | I/O  | Command and byte enables                                                                                                                                                                                                       |

|             | pci_cbe[5]#    | P31   | I/O  | Command and byte enables                                                                                                                                                                                                       |

|             | pci_cbe[6]#    | M34   | I/O  | Command and byte enables                                                                                                                                                                                                       |

|             | pci_cbe[7]#    | R29   | I/O  | Command and byte enables                                                                                                                                                                                                       |

|             | pci_clk        | AB34  | I    | PCI input clock                                                                                                                                                                                                                |

|             | pci_clk_out    | AB32  | 0    | PCI output clock                                                                                                                                                                                                               |

|             | pci_devsel#    | U34   | I/O  | Device select                                                                                                                                                                                                                  |

|             | pci_frame#     | W31   | I/O  | Frame number request                                                                                                                                                                                                           |

|             | pci_gnt#       | AC30  | I    | Bus grant                                                                                                                                                                                                                      |

|             | pci_idsel      | AA30  | I    | IDSEL signal                                                                                                                                                                                                                   |

|             | pci_inta#      | AC32  | I/O  | Interrupt A. Used to request an interrupt                                                                                                                                                                                      |

|             | pci_intb#      | AC34  | I    | Interrupt B. Used to request an interrupt in a multi-function device                                                                                                                                                           |

|             | pci_intc#      | AC31  | I    | Interrupt C. Used to request an interrupt in a multi-function device                                                                                                                                                           |

|             | pci_intd#      | AC33  | I    | Interrupt D. Used to request an interrupt in a multi-function device                                                                                                                                                           |

|             | pci_irdy#      | V32   | I/O  | Initiator ready                                                                                                                                                                                                                |

|             | pci_m66en      | R32   | I    | Enable 66MHz. Indicates whether the bus segment is operating at 66 MHz or 33MHz                                                                                                                                                |

|             | pci_par        | V31   | I/O  | Parity                                                                                                                                                                                                                         |

|             | pci_par64      | P29   | I/O  | Parity on pci_ad[63:32]                                                                                                                                                                                                        |

|             | pci_pcix_133#  | G31   | I    | Enable 133 Mhz                                                                                                                                                                                                                 |

|             | pci_pcix_mode# | H30   | I    | Indicates PCI-X mode                                                                                                                                                                                                           |

|             | pci_perr#      | U32   | I/O  | Parity error                                                                                                                                                                                                                   |

|             | pci_req#       | AA34  | 0    | Bus request                                                                                                                                                                                                                    |

|             | pci_req64#     | R30   | I/O  | Request 64-bit transfer                                                                                                                                                                                                        |

|             | pci_rst#       | AB33  | I/O  | PCI reset. This pin must be pulled down to Vss with a 4.7K resistor when PCI is configured as host. When the device is configured for standalone, non-PCI mode, it should be driven to logic 0 by external logic or pull-down. |

|             | pci_sel_pci32  | H31   | I    | Indicates 32-bit-only mode. Upper 32 bits and associated signals are disabled.                                                                                                                                                 |

|             | pci_serr#      | T34   | I/O  | System error                                                                                                                                                                                                                   |

|             |                |       |      |                                                                                                                                                                                                                                |

Version 1.7

2-10

Last modified: 07/12/2006

Table 2-1 S5610 Signal Description (alphabetic within ports)

| Port          | Signal Name    | Pin # | Type | Description                                                                                                                                                                                                                                    |

|---------------|----------------|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCI (cont.)   | pci_stop#      | W29   | I/O  | PCI stop                                                                                                                                                                                                                                       |

|               | pci_trdy#      | W30   | I/O  | Target ready                                                                                                                                                                                                                                   |

| PLL           | pll_refclk     | E34   | I    | Clock for PLL1. Used internally to generate the SDRAM clock                                                                                                                                                                                    |

|               | pll2_refclk    | F33   | Ι    | Clock for PLL2. Used internally to generate the HP (processor) and LP clocks                                                                                                                                                                   |

| SPI           | spi_cs[0]#     | AG29  | 0    | Chip select                                                                                                                                                                                                                                    |

|               | spi_cs[1]#     | AH34  | 0    | Chip select                                                                                                                                                                                                                                    |

|               | spi_cs[2]#     | AJ33  | 0    | Chip select                                                                                                                                                                                                                                    |

|               | spi_cs[3]#     | AH32  | 0    | Chip select                                                                                                                                                                                                                                    |

|               | spi_cs[4]#     | AH31  | 0    | Chip select                                                                                                                                                                                                                                    |

|               | spi_cs[5]#     | AJ34  | 0    | Chip select                                                                                                                                                                                                                                    |

|               | spi_cs[6]#     | AH28  | 0    | Chip select                                                                                                                                                                                                                                    |

|               | spi_cs[7]#     | AJ32  | 0    | Chip select                                                                                                                                                                                                                                    |

|               | spi_sck        | AG30  | 0    | SPI clock                                                                                                                                                                                                                                      |

|               | spi_si         | AF28  | I    | Serial data in                                                                                                                                                                                                                                 |

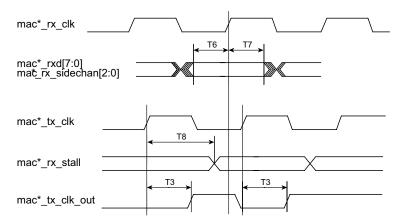

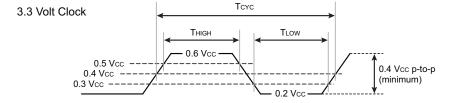

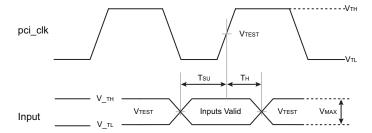

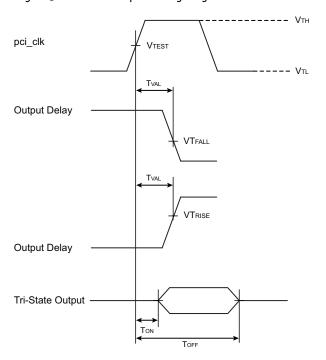

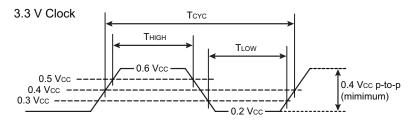

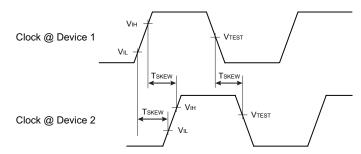

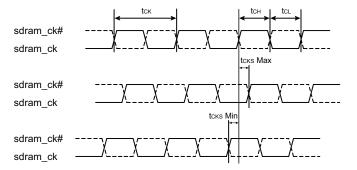

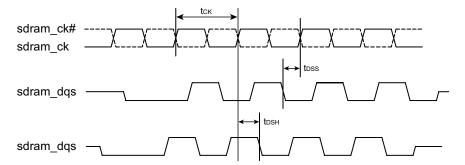

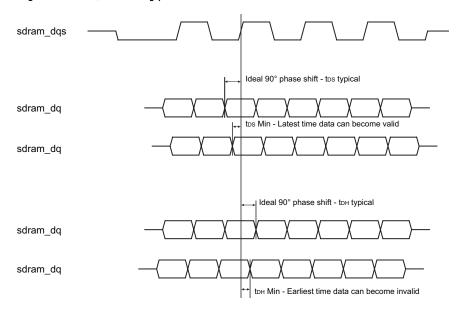

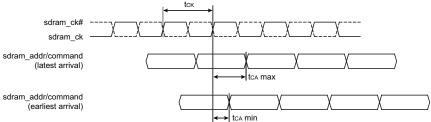

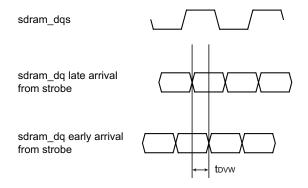

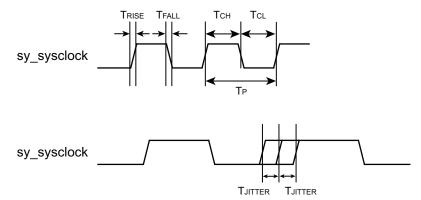

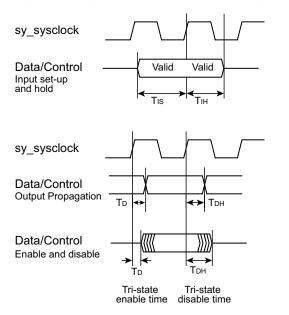

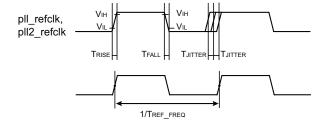

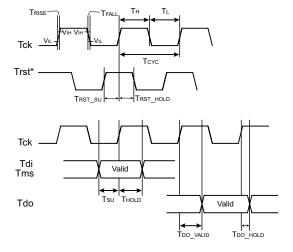

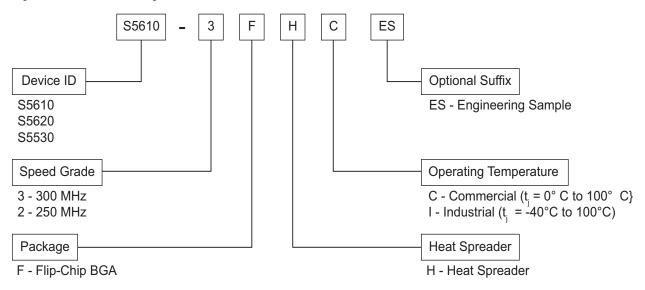

|               | spi_so         | AH33  | 0    | Serial data out                                                                                                                                                                                                                                |